qSlot

Saha koşullarında çalışan endüstriyel IoT sistemleri (özellikle akıllı tarım gibi bakım pencerelerinin kısıtlı, arıza maliyetinin yüksek olduğu uygulamalar) zamanla aynı temel problem etrafında birikir: fonksiyonlar arttıkça kablolama, arayüz çeşitliliği ve servis süreçleri yönetilemez hale gelir. Taşıyıcı kart üzerinde farklı haberleşme modülleri (GSM/LTE, LoRa, Wi‑Fi), sensör arayüzleri, IO genişletmeleri ve güç dönüştürücüler birlikte konumlandıkça, her bir yeni ihtiyaç çoğu zaman yeni bir anakart revizyonunu, sahada daha fazla elle müdahaleyi ve daha uzun arıza tespit sürelerini tetikler.

qSlot, bu karmaşıklığı tek bir prensiple azaltmayı hedefler: fonksiyonları kalıcı kablo demetleri ve tekil anakart tasarımları yerine standart bir tak‑çıkar modül yuvası üzerinden yönetmek. Böylece sistem, sahada kart değişimiyle hızlı servis edilebilir; yeni fonksiyonlar aynı mekanik ve elektriksel arayüzü kullanarak modül seviyesinde eklenebilir; platform büyüdükçe hem üretim hem de bakım süreçleri öngörülebilir ve ölçeklenebilir kalır.

qSlot, açık kaynak bir ekosistem olacak şekilde; üçüncü tarafların da aynı fiziksel/elektriksel arayüz ile modül geliştirebilmesini amaçlar.

Nedir, ne değildir?

qSlot, sahada modülerlik sağlamak amacıyla tanımlanmış bir slot standardıdır. Buradaki “standart” kelimesi, tek tek modüllerin herhangi bir yuvaya takılabildiği evrensel bir uyumluluğu değil; belirli bir sistem mimarisi içinde, her yuvanın rolünün ve kabul edeceği modül sınıfının baştan tanımlandığı kontrollü bir ekosistemi ifade eder.

Bu yaklaşımda yuvalar “genel amaçlı” değildir. Örneğin bir IoT haberleşme yuvası, yalnızca GSM/LTE, LoRa veya Wi‑Fi/BLE gibi haberleşme modüllerini kabul edecek şekilde tasarlanır; güç seviyeleri (örn. VCC sınıfı), enable sinyalleri ve beklenen arayüzler bu rol üzerinden sabitlenir. Böylece sahada yanlış modül eşleşmelerinin, belirsiz güç beklentilerinin ve servis sırasında hatalı müdahalelerin önüne geçilir.

qSlot’un PCIe ile ilişkisi yalnızca mekaniktir. PCIe Mini Card (Mini PCIe) konektörünü ve form faktörünü; yüksek bulunabilirlik, olgun ekosistem ve sağlam mekanik kilitleme avantajları nedeniyle kullanır. Ancak qSlot PCIe protokolünü uygulamaz; PCIe lane eşlemesi, enumerasyon veya PCIe cihaz uyumluluğu hedeflenmez. Bu doküman, qSlot konektörü üzerinde özel bir pin haritası tanımlar ve bu pinler üzerinden güç, kontrol sinyalleri ve yaygın çevre birimleri arayüzleri (I2C/SPI/UART vb.) için modüler bir elektriksel arayüz sunar.

qSlot konektörü PCIe Mini Card’a benzer görünebilir; ancak PCIe cihazları (ör. Mini PCIe Wi‑Fi kartı) qSlot’a takılsa bile çalışmaz. qSlot yalnızca bu spesifikasyonda tanımlanan pin haritası ve slot sınıfları ile uyumludur.

Kapsam

Bu doküman, qSlot v1.0’ın normatif teknik tanımını sunar; yani taşıyıcı kart ve modül tasarımlarının birlikte çalışabilir olması için gerekli minimum kuralları ve sınırları belirler. Tanımın odağı, “hangi modül ne yapar?” sorusundan ziyade, modüllerin sahada güvenilir şekilde tak‑çıkar çalışabilmesi için ortak arayüzün nasıl yapılandırılacağıdır.

Bu kapsamda doküman; PCIe Mini Card form faktörünün qSlot içinde nasıl kullanıldığını, soket seçimi ve mekanik yükseklik kısıtlarını, pin haritasını ve pinlerin fonksiyon sınıflarını (güç, kontrol, haberleşme, analog/dijital IO) tanımlar. Buna ek olarak; güç hatlarının beklenen kullanım modelini (3V3/VCC/POWER_FEED), enable sinyallerinin standart davranışını (PWR_EN ve COMM_EN), domain kurallarını ve sahada tekrarlanabilir tasarımlar için minimum ESD/EMI ve geri besleme (backfeed) önleme ilkelerini açıklar.

Bilinçli olarak kapsam dışında bırakılan konular ise, arayüzün üzerinde inşa edilen katmanlardır: her bir modülün iç donanım tasarımı ve BOM’u, taşıyıcı kartın sistem mimarisi (CPU seçimi, güç topolojisi, backplane yerleşimi), ayrıca yazılım/firmware sürücüleri ve üst seviye protokol anlaşmaları. Bu başlıklar, qSlot arayüzünü referans alan ayrı modül dokümanlarında ve platform dokümantasyonunda tanımlanmalıdır.

Bu dokümanda “MUST / MUST NOT / SHOULD / MAY” gibi ifadeler, uyumluluk için bağlayıcı veya öneri niteliğinde kuralları belirtir. Uygulama dokümanları bu kuralları genişletebilir; ancak qSlot v1.0 uyumluluğunu bozacak şekilde daraltmamalıdır.

Terimler ve kısaltmalar

Bu bölüm, qSlot v1.0 dokümanında tekrar eden kavramları tek bir yerde toplayarak yanlış yorumu azaltmayı amaçlar. Terimler, doküman boyunca aynı anlamda kullanılmak üzere burada sabitlenmiştir.

- qSlot: PCIe Mini Card form faktörünü kullanan; ancak elektriksel pin haritası ve davranışları bu dokümanda tanımlanan modüler slot standardı.

- Mini Card / Mini PCIe: qSlot’un yalnızca mekanik olarak faydalandığı PCIe Mini Card konektör ve kart form faktörü ailesi.

- Carrier (Taşıyıcı kart): Bir veya daha fazla qSlot yuvasını barındıran; platformun güç/işlemci/ana arayüz altyapısını taşıyan ana kart.

- Module (Modül): Belirli bir fonksiyonu gerçekleştirmek üzere qSlot yuvasına takılan, tak‑çıkar çalışması hedeflenen fonksiyon kartı.

- Slot (Yuva): Carrier üzerinde yer alan tek bir qSlot konektör pozisyonu.

- Slot class (Yuva sınıfı): Bir yuvanın rolünü ve sabit parametrelerini (özellikle VCC seviyesi gibi) tanımlayan sınıflandırma. “Hangi modül hangi yuvaya?” eşleşmesini belirler.

- Domain (Voltaj domain’i): Seviye tanımının referans aldığı besleme alanı (örn. 3V3 domain). Dijital arayüz seviyeleri domain’e göre değerlendirilir.

- Enable (Etkinleştirme) sinyali: Bir fonksiyonun kontrollü açılıp kapanmasını sağlayan kontrol hattı. qSlot’ta PWR_EN ve COMM_EN bunun için tanımlanır.

- Hot‑plug / Tak‑çıkar: Sistem enerjiliyken modülün takılması/çıkarılması senaryosu. qSlot, bu senaryoda oluşabilecek backfeed ve bus kararsızlıklarını azaltacak kurallar içerir.

- Backfeed (Geri besleme): Modülün, 3V3/VCC gibi besleme hatlarını istenmeden taşıyıcı karta doğru beslemesi.

Bu dokümanda kullanılan “MUST / MUST NOT / SHOULD / MAY” ifadeleri, uyumluluk için bağlayıcı veya öneri niteliğindeki kuralları belirtir.

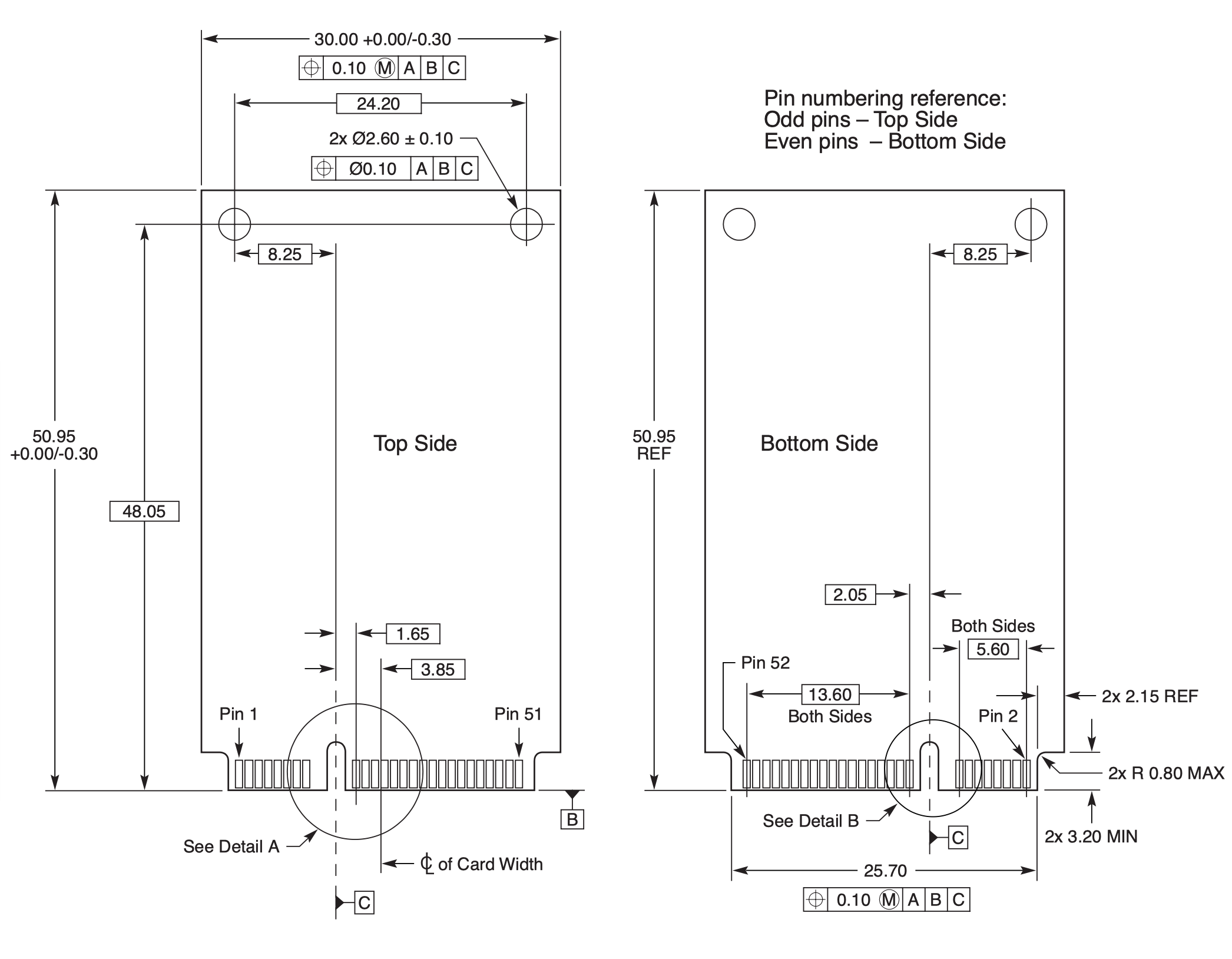

Kart ebat standartları

qSlot, mekanik tarafta PCIe Mini Card ekosisteminin olgunlaşmış üretim altyapısından faydalanır. Bu nedenle kart ebatları ve montaj yönleri, Mini Card ailesinin yaygın pratiklerine paralel biçimde tanımlanır. Buradaki amaç, modül tasarımcılarının tek bir “mekanik dil” üzerinden ilerleyebilmesi ve taşıyıcı kart tarafında yuva yerleşimi/servis erişimi gibi kararların öngörülebilir kalmasıdır.

Bu dokümanda dört temel form tanımlanır: Full/Half uzunluk, ve her birinin Single/Double dizgi seçeneği. “Single/Double” ifadesi elektriksel bir farklılık yaratmaz; yalnızca modül üzerinde komponent yerleşiminin tek yüz veya çift yüz yapılabilmesini tarif eder.

| Standart | Kartı Adı | Açıklama | Ebat |

|---|---|---|---|

| F1 | Full Mini Double | iki tarafı dizgili (full) | 50.95 x 30 mm |

| F2 | Full Mini Single | tek tarafı dizgili (full) | 50.95 x 30 mm |

| H1 | Half Mini Double | iki tarafı dizgili (half) | 26.80 x 30 mm |

| H2 | Half Mini Single | tek tarafı dizgili (half) | 26.80 x 30 mm |

qSlot ekosisteminde hedeflenen saha dayanımı ve komponent çeşitliliği göz önüne alındığında, modüller pratikte çoğunlukla çift yüz dizgili kabul edilerek tasarlanır ve buna uygun yüksek yapılı Mini Card soketleri üzerinden taşınır. Tek yüz dizgi kararı, yalnızca mekanik yükseklik veya üretim kısıtları bunu gerektirdiğinde tercih edilmelidir.

Konnektör ve mekanik kısıtlar

qSlot, Mini Card ailesinin ana avantajlarından biri olan key geometrisini kullanır; bu sayede kartın fiziksel olarak yanlış yönde takılması yapısal olarak engellenir. Bununla birlikte, saha güvenilirliğini asıl belirleyen unsur soket seçimiyle oluşan kart‑kart mesafesi ve buna bağlı komponent yükseklik zarfıdır. Bu nedenle, taşıyıcı kart üzerinde kullanılacak soket ailesi seçilirken modülün alt/üst yüzündeki maksimum komponent yüksekliği daha ilk tasarım aşamasında hedeflenmelidir.

Örnek bir referans olarak TE Connectivity 1775862‑2 soketi kullanıldığında; modülün alt yüzünde izin verilen maksimum komponent yüksekliği 1.35 mm olarak kabul edilir. Bu koşul sağlandığında modül ile taşıyıcı kart arasında yaklaşık 1.45 mm serbest boşluk oluşur ve tipik kart‑kart mesafesi ~2.8 mm seviyesindedir. Bu değerler, modül tasarımında footprint seçimi, komponent yerleşimi ve mekanik tolerans analizinde “tasarım girdisi” olarak ele alınmalıdır.

Alt yüzünde yüksek komponent gerektiren modüller için standart soket seçimi yeterli olmayabilir. Bu senaryolarda daha yüksek soket ailesi seçilmeli veya modül mimarisi tek yüz dizgiye yönlendirilmelidir; aksi durumda saha titreşimi ve tolerans birikimi altında temas riski artar.

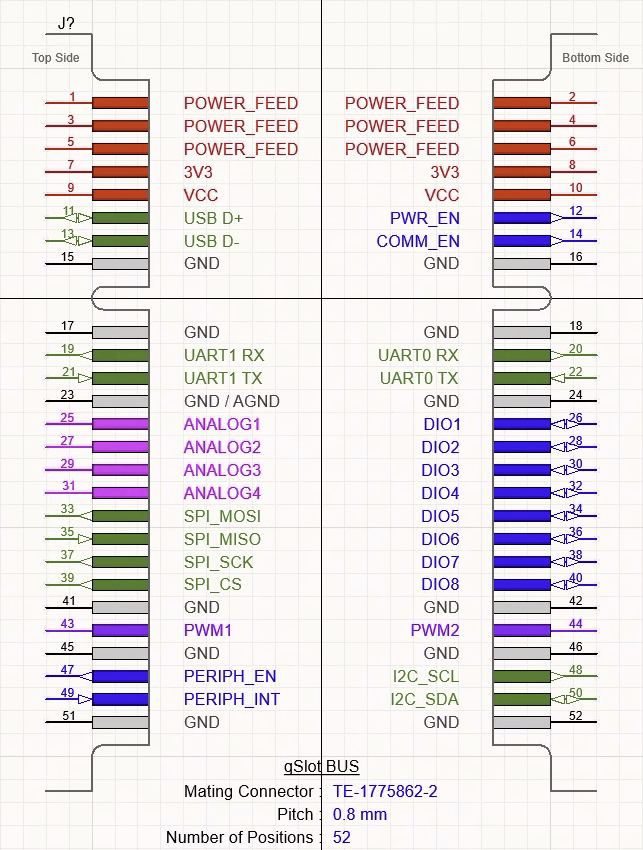

Pin haritası (qSlot v1.0)

Bu bölüm, qSlot konektörü üzerinde tanımlanan pinlerin fiziksel konumunu ve bu pinlerin hangi işlev sınıfına ait olduğunu tarif eder. Pin haritası, modül ve taşıyıcı kart tasarımlarının aynı arayüz üzerinden birlikte çalışabilmesi için referans alınacak ana kaynaktır.

Pin detayları (elektriksel limitler, varsayılan durumlar, pull‑up/down önerileri, ESD/EMI önlemleri) bu dokümanın ilgili alt bölümlerinde ve gerektiğinde “Pin Description” sayfalarında genişletilir. Bu tabloda amaç, konum ve isimlendirmeyi sabitlemektir.

Pin konum tablosunu göster (metin)

| Top Side | Pin ID | Pin ID | Bottom Side |

|---|---|---|---|

| POWER_FEED | 01 | 02 | POWER_FEED |

| POWER_FEED | 03 | 04 | POWER_FEED |

| POWER_FEED | 05 | 06 | POWER_FEED |

| 3V3 | 07 | 08 | 3V3 |

| VCC | 09 | 10 | VCC |

| USB_D+ | 11 | 12 | PWR_EN |

| USB_D- | 13 | 14 | COMM_EN |

| GND | 15 | 16 | GND |

| — | Key | Key | — |

| GND | 17 | 18 | GND |

| UART1_RX | 19 | 20 | UART0_RX |

| UART1_TX | 21 | 22 | UART0_TX |

| GND | 23 | 24 | GND |

| ANALOG1 | 25 | 26 | DIO1 |

| ANALOG2 | 27 | 28 | DIO2 |

| ANALOG3 | 29 | 30 | DIO3 |

| ANALOG4 | 31 | 32 | DIO4 |

| SPI_MOSI | 33 | 34 | DIO5 |

| SPI_MISO | 35 | 36 | DIO6 |

| SPI_SCK | 37 | 38 | DIO7 |

| SPI_CS | 39 | 40 | DIO8 |

| GND | 41 | 42 | GND |

| PWM1 | 43 | 44 | PWM2 |

| GND | 45 | 46 | GND |

| PERIPH_EN | 47 | 48 | I2C_SCL |

| PERIPH_INT | 49 | 50 | I2C_SDA |

| GND | 51 | 52 | GND |

Pin segmentleri ve işlevsel sınıflar

Pinler, arayüzün okunabilirliğini artırmak ve modül tasarımında “hangi sinyal hangi amaçla kullanılır?” sorusunu netleştirmek için segmentlere ayrılmıştır. Segment tanımı, hem pinlerin işlevsel rolünü hem de tasarımcıdan beklenen temel kullanım kurallarını özetler.

Güç dağıtımı

Bu segment; modül beslemeleri ve yüksek akım aktarımı için ayrılmıştır.

- 3V3: qSlot üzerindeki standart dijital domain beslemesi.

- VCC: slot class ile sabitlenen yardımcı besleme (örn. 3V8, 5V).

- POWER_FEED: 1A üzeri ihtiyaçlar için paralel pinli yüksek akım hattı.

Tasarım ilkesi: güç segmenti pinleri, taşıyıcı kartta düşük empedanslı dağıtım ve yeterli dönüş yolu ile desteklenmelidir.

Segment kısa adı: PWR

Güç ve iletişim kontrolü

Bu segment, modülün sahada yönetilebilir olmasını sağlayan iki temel kontrol sinyalini tanımlar.

- PWR_EN: modülün (varsa) güç anahtarlamasını etkinleştirir.

- COMM_EN: buffer/level‑shifter dahil iletişim yolunu etkinleştirir.

Tasarım ilkesi: qSlot v1.0 için bu hatlar aktif HIGH kabul edilir; ters aktif ihtiyacı modül üzerinde çözülmelidir.

Segment kısa adı: CTRL

Haberleşme kanalları

Bu segment; yaygın çevre birimi arayüzlerini aynı konektör üzerinden modüler kılmak için ayrılmıştır.

- UART0: ana 3V3 UART kanalı (genel amaç).

- UART1: yardımcı UART kanalı (özel domain veya ikinci kanal).

- I2C_SCL / I2C_SDA: master I2C hattı (3V3).

- SPI_MOSI / SPI_MISO / SPI_SCK / SPI_CS: 3V3 SPI hattı.

- USB_D+ / USB_D-: opsiyonel servis/test USB veri hatları.

Tasarım ilkesi: I2C kullanılan modüllerde buffer zorunludur; SPI_CS yalnızca chip‑select amaçlı kullanılmalıdır.

Segment kısa adı: COMM

Analog ölçüm hatları

Bu segment, analog ölçüm gerektiren modüller için ayrılmıştır.

- ANALOG1..4: 3V3 referanslı analog hatlar.

Tasarım ilkesi: analog hatlar dijital IO yerine kullanılmaz; hat yönlendirmesi gürültülü bölgelerden uzak tutulur.

Segment kısa adı: ANALOG

Genel amaçlı IO ve PWM

Bu segment, modül bazlı kontrol ve zamanlama ihtiyaçlarını karşılar.

- DIO1..8: 3V3 dijital IO hatları.

- PWM1..2: 3V3 PWM hatları.

Tasarım ilkesi: bu pinler modül dokümanında açıkça “input/output” yönü ve varsayılan durumuyla tanımlanmalıdır.

Segment kısa adı: DIO/PWM

Dönüş referansı

Bu segment, güç ve sinyaller için ortak dönüş/şasi referansını sağlar.

- GND: toplam 12 pin ile düşük empedanslı dönüş yolu hedeflenir.

Tasarım ilkesi: yüksek akım hatlarında dönüş pinleri yakın ve paralel kullanılmalı; analog ölçümlerde analog pinlere komşu GND pinleri tercih edilmelidir.

Segment kısa adı: GND

Güç mimarisi

qSlot güç mimarisi, modüllerin sahada tak‑çıkar çalışabilmesini desteklemek için iki temel hedefe göre kurgulanır: (1) dijital domain’i her modülde öngörülebilir kılmak ve (2) modül tiplerine göre değişen besleme ihtiyaçlarını slot class ile belirsizlikten çıkarmak. Bu nedenle qSlot üzerinde üç güç sınıfı tanımlanır: sabit 3V3, yuva sınıfına bağlı VCC, ve yüksek akım ihtiyacı için POWER_FEED.

3V3

3V3 hattı, qSlot ekosistemindeki tüm temel dijital arayüzlerin referans domain’idir. UART0/I2C/SPI/DIO/PWM gibi hatların seviye tanımı bu besleme üzerinden sabitlenir; bu sayede modüller arasında seviye uyumsuzluğu riski azaltılır.

| Özellik | Değer |

|---|---|

| Uzun Adı | DIGITAL_3V3 |

| Kısa Adı | 3V3 |

| Voltaj Seviyesi | 3.3 V (sabit) |

| Max Sürekli Akım | 1 A (modül çıkışı 2 pin toplamı) |

3V3 hattı “yük taşımak” için değil, dijital domain’i tutarlı kılmak için tanımlanmıştır. Modül üzerinde yüksek akım gerektiren yükler (motor sürücü, röle bobini, ısıtıcı vb.) mümkünse POWER_FEED veya VCC üzerinden beslenmelidir.

POWER_FEED

POWER_FEED, 1A üzeri güç gerektiren modüller için ayrılmış yüksek akım besleme sınıfıdır. Bu hat, konektör üzerinde paralel pinler kullanılarak toplam akım kapasitesi artırılacak şekilde planlanmıştır. POWER_FEED’in voltaj seviyesi qSlot tarafından sabitlenmez; taşıyıcı kartın ve ilgili slot class’ın tanımına bağlıdır.

| Özellik | Değer |

|---|---|

| Uzun Adı | HIGH_CURRENT_POWER_FEED |

| Kısa Adı | POWER_FEED |

| Voltaj Seviyesi | Slot/Carrier tarafından tanımlı |

| Max Sürekli Akım | 3 A (paralel pin toplamı hedef) |

Mini Card konektörlerinde pin başına akım kapasitesi, konektör serisine, kontak malzemesine ve sıcaklık artışına göre değişir. POWER_FEED pinleri paralel kullanılsa dahi, gerçek kapasite taşıyıcı kartın bakır genişliği/kalınlığı, via sayısı ve dönüş yolunun empedansı ile sınırlanabilir. Carrier tasarımında akım paylaşımı ve ısıl analiz yapılması SHOULD kabul edilir.

VCC

VCC, modülün fonksiyonuna bağlı olarak ihtiyaç duyduğu yardımcı besleme hattıdır (örn. GSM 3V8, röle 5V). VCC, “keyfi değişken bir pin” değildir; her bir qSlot yuvası için slot class kapsamında tek bir seviyeye sabitlenir ve bu bilgi hem dokümantasyonda hem de taşıyıcı kart üzerinde etiketlenir. Bu yaklaşım, yanlış modül eşleşmelerinde oluşabilecek hasarı ve belirsiz güç beklentilerini azaltır.

| Özellik | Değer |

|---|---|

| Uzun Adı | VCC |

| Kısa Adı | VCC |

| Voltaj Seviyesi | Slot class ile sabit (örn. VCC3V8, VCC5V0) |

| Max Sürekli Akım | 1 A (modül çıkışı 2 pin toplamı) |

Taşıyıcı kart üzerinde her qSlot yuvası için VCC seviyesi kalıcı olarak belirtilmelidir (örn. VCC=3V8). Slot class bilgisi saha servisinde “doğru modül‑doğru yuva” eşleşmesi için kritik kabul edilir.

VCC/3V3 hatlarının modül tarafından taşıyıcı karta geri beslenmesi istenmeyen bir durumdur. Modül üzerinde yerel regülatör/boost gibi kaynaklar bulunuyorsa, geri akım yolları için ideal diyot/ORing veya güç anahtarı kullanımı SHOULD değerlendirilmelidir.

Enable sinyalleri (standart davranış)

qSlot, sahada servis edilebilirlik ve enerji yönetimi açısından modüllerin “takılı ama kontrollü” şekilde çalıştırılabilmesini hedefler. Bu nedenle güç ve haberleşme yolları için iki adet enable sinyali tanımlar. Bu sinyaller, modül üzerinde bulunan güç anahtarlama elemanlarını ve/veya iletişim tamponlarını (buffer/level‑shifter) kontrol etmek için kullanılır.

qSlot v1.0’da enable sinyallerinin mantığı aktif HIGH olarak standardize edilmiştir. Taşıyıcı kart, reset sonrası bu hatları bilinen bir durumda tutabilmeli; modül ise enable hattı aktif değilken geri besleme veya “yarı açık” çalışma durumları üretmemelidir.

| Sinyal | Amaç | Varsayılan mantık | Not |

|---|---|---|---|

| PWR_EN | Modülün (varsa) güç anahtarlamasını etkinleştirir | Aktif HIGH | Modül güç katmanı bu sinyale bağlıysa, enable=LOW iken modülün yükleri beslememesi MUST kabul edilir |

| COMM_EN | Haberleşme yolunu (buffer/level‑shifter dahil) etkinleştirir | Aktif HIGH | Enable=LOW iken modülün haberleşme hatlarını sürmemesi MUST kabul edilir |

Ters aktif (active‑low) davranışa ihtiyaç duyan modüller, invert işlemini modül üzerinde çözmelidir. Carrier tarafında enable sinyallerinin polaritesi değiştirilmez; böylece platform genelinde servis ve entegrasyon davranışı tutarlı kalır.

UART kanalları

qSlot, sahada en sık karşılaşılan haberleşme modüllerini (GSM/LTE, Wi‑Fi/BLE, GNSS, RS‑485 köprüleri vb.) ortak bir arayüz üzerinden yönetebilmek için iki adet UART kanalı tanımlar. Bu kanalların amacı “iki modül aynı anda seri haberleşsin” gibi genel bir paralellik hedeflemekten ziyade; platformun servis, test ve entegrasyon senaryolarında esneklik sağlamaktır.

Bu nedenle qSlot v1.0’da UART0, platformun birincil seri haberleşme hattı olarak kabul edilir ve voltaj domain’i 3V3 sabittir. Taşıyıcı kart tarafında UART0, mümkün olduğunca her platformda erişilebilir olmalı ve modül dokümanlarında varsayılan seri port olarak referans alınmalıdır. UART1 ise ikincil/yardımcı kanal olarak ayrılmıştır; üretim testi, debug amaçlı ikinci port, ya da farklı seviye gerektiren modüller için (slot class veya modül tasarımına bağlı) ayrı bir domain’de kullanılabilir.

| Kanal | Rol | Voltaj domain |

|---|---|---|

| UART0 | Birincil seri haberleşme hattı | 3V3 (sabit) |

| UART1 | Yardımcı/test/özel seviye hattı | Slot class veya modüle göre |

- Bir modül seri haberleşme için tek bir UART kullanacaksa, varsayılan tercih UART0 MUST kabul edilir.

- UART1 kullanımı, yalnızca platform dokümanında gerekçelendirilmiş bir ihtiyaç varsa SHOULD kabul edilir.

Bu dokümanda UART hatları UART0_TX/UART0_RX ve UART1_TX/UART1_RX olarak adlandırılır. Şematik/PCB sembollerinde farklı kısaltmalar kullanılmamalıdır.

I2C master bus

qSlot, taşıyıcı karttan modüllere dağıtılan tek bir master I2C omurgası tanımlar. Bu omurga; düşük hız, çoklu periferi ve saha servisinde erişilebilirlik avantajları nedeniyle özellikle sensör, IO genişletici, ölçüm entegresi gibi modüllerde tercih edilir. I2C hattı qSlot üzerinde 3V3 domain’de taşınır ve fiziksel olarak ortak bir bus olduğu için hem adres çakışması hem de hot‑plug / güç anahtarlama senaryolarında özel önlemler gerektirir.

Bu nedenle qSlot v1.0’da, I2C kullanan her modülde bus izolasyonu ve yeniden sürme (re‑drive) amacıyla I2C buffer kullanımı MUST kabul edilir. Buffer; modül takılı değilken bus’ın “açıkta kalmasını” engeller, modül enerji verilmediğinde hatların geri besleme yolu olmasını azaltır ve sistemde birden fazla I2C modülü kullanıldığında adres/segment yönetimini mümkün kılar.

| Özellik | Değer |

|---|---|

| Hatlar | I2C_SCL, I2C_SDA |

| Voltaj | 3V3 |

| Topoloji | Ortak master bus |

| Yön | Çift yönlü (bidirectional) |

I2C hattının pull‑up dirençleri ve toplam bus kapasitansı, taşıyıcı kartın topolojisine ve aynı anda takılı modül sayısına bağlıdır. Pull‑up değerleri “her modül kendi pull‑up’ını koysun” yaklaşımıyla çoğaltılmamalı; platform seviyesinde kontrol edilmelidir.

PERIPH_EN ve PERIPH_INT

qSlot, yalnızca I2C’ye özel olmayan iki adet periferi kontrol hattı tanımlar. Bu hatlar, modül üzerindeki sensör/entegre gibi alt bileşenlerin enable ve interrupt ihtiyaçlarını ortak bir dil ile karşılamak için eklenmiştir.

- PERIPH_EN (3V3): Modül üzerindeki belirli bir periferi (ör. sensör, I/O expander, ölçüm IC) için enable hattı.

- PERIPH_INT (3V3): Periferinin taşıyıcı karta bildirim/interrupt çıkışı.

Bu iki hat, I2C dışındaki periferi senaryolarında da kullanılabilir; ancak modül dokümanında hangi bileşene bağlı olduğu ve varsayılan davranışı açıkça belirtilmelidir.

Bu hatları yalnızca I2C’ye özel adlandırmak, SPI/UART gibi farklı periferi topolojilerinde gereksiz bir kısıt yaratır. PERIPH_EN/PERIPH_INT isimleri; arayüzü, periferi türünden bağımsız olacak şekilde daha doğru temsil eder.

SPI bus

qSlot, daha yüksek hız ve deterministik zamanlama gerektiren çevre birimleri için 3V3 seviyesinde bir SPI arayüzü sağlar. SPI hattı, özellikle ADC/DAC, hızlı IO genişleticiler, harici bellekler ve bazı RF çevre birimleri gibi I2C’ye kıyasla daha yüksek bant genişliği veya daha düşük gecikme beklenen modüllerde tercih edilir.

SPI arayüzü, qSlot üzerinde aşağıdaki sinyallerden oluşur:

- SPI_MOSI: master → slave veri

- SPI_MISO: slave → master veri

- SPI_SCK: saat

- SPI_CS: chip‑select (aktif LOW varsayımı modül dokümanında açıkça belirtilmelidir)

SPI_CSyalnızca chip‑select amaçlıdır; RESET/ICSP gibi farklı işlevlerle yeniden kullanılmaz.- Çoklu SPI modülü senaryolarında, her modül kendi chip‑select hattını kullanmalı; ortak CS paylaşımı yapılmamalıdır.

- Seviye dönüştürme ihtiyacı olan modüller (1V8 vb.) bu dönüşümü modül üzerinde çözmelidir; platform domain’i 3V3 olarak sabittir.

Analog hatlar (ANALOG1..4)

qSlot, taşıyıcı kart üzerindeki ADC kaynaklarını modüllere açmak için 4 adet analog hat tanımlar. Bu hatlar; sensör analog çıkışları, referanslı ölçümler veya düşük bant genişlikli analog sinyaller için tasarlanmıştır. Analog hatlar, dijital IO olarak yeniden amaçlandırılmaz; böylece hem hat yönlendirme stratejisi hem de filtreleme/koruma varsayımları platform genelinde tutarlı kalır.

Analog hatlar, 3V3 domain’e referanslı olarak düşünülür. Gerçek ölçüm aralığı (örn. 0–3.3V), ADC referans mimarisi ve giriş filtre topolojisi taşıyıcı kart tarafından belirlenir ve platform dokümanında ayrıca tanımlanmalıdır. Modül tarafı ise bu arayüze uyumlu olacak şekilde çıkış aralığını, kaynak empedansını ve koruma elemanlarını tasarlamalıdır.

| Özellik | Değer |

|---|---|

| Hatlar | ANALOG1..4 |

| Referans | 3V3 domain |

| Kullanım | sensör analog çıkışı / düşük hız analog ölçüm |

- Modül, ANALOG hatlarına yalnızca analog seviye uygular; PWM/1‑wire/bit‑bang gibi dijital yeniden kullanım MUST NOT kabul edilir.

- Modül analog çıkışı, taşıyıcı kartın giriş filtrelemesi ve ADC örnekleme kondansatörü nedeniyle oluşabilecek anlık akım çekişini tolere edebilmelidir; yüksek kaynak empedanslı sensörlerde modül üzerinde buffer/RC şartlandırma SHOULD değerlendirilmelidir.

- Taşıyıcı kart, ANALOG hatlarında giriş koruması (ESD ve makul seviyede aşırı gerilim kısma) sağlamalıdır; modül tarafında da saha kablolamasına yakın analog kaynaklar varsa ek koruma MAY uygulanabilir.

Analog hatlar; yüksek akım/gürültülü hatlardan uzak, kısa ve korumalı şekilde yönlendirilmelidir. POWER_FEED/VCC anahtarlama bölgeleri, RF hatları ve hızlı kenarlı dijital hatlardan kaçınılmalı; mümkünse analog hatlara komşu GND pinleri dönüş yolu olarak kullanılmalıdır.

Dijital IO hatları (DIO1..DIO8)

qSlot, modül bazlı kontrol/IO ihtiyaçları için 8 adet 3V3 dijital IO hattı tanımlar. Bu hatlar; röle sürme, durum okuma, basit kontrol sinyalleri ve düşük/orta hızda dijital arayüzler için “genel amaçlı” bir alan sağlar.

Bir modülün 8 adetten fazla IO ihtiyacı varsa, bu ihtiyacın doğrudan daha fazla pin tanımlayarak genişletilmesi yerine I2C üzerinden IO expander (veya benzer bir çevre birimi) ile çözülmesi önerilir. Bu yaklaşım, konektör pin haritasını sabit tutarak geriye uyumluluğu korur ve aynı zamanda IO sayısının modül ölçeğinde esnek biçimde artırılmasını sağlar.

| Özellik | Değer |

|---|---|

| Hatlar | DIO1..DIO8 |

| Voltaj | 3V3 |

| Yön | giriş/çıkış (modüle göre) |

PWM hatları (PWM1..PWM2)

qSlot, zamanlama veya görev çevrimi kontrolü gerektiren senaryolar için iki adet PWM hattı sağlar. Bu hatlar; fan sürme, LED dimming, basit motor/valf kontrolü, darbe üretimi veya taşıyıcı kart üzerindeki zamanlayıcı kaynaklarına doğrudan erişim gibi ihtiyaçlarda kullanılabilir.

PWM hatlarının sayısı bilinçli olarak iki ile sınırlandırılmıştır; amaç, konektör pin haritasını büyütmeden sahada en yaygın ihtiyaçları karşılamaktır. Bir modülün ikiden fazla PWM kanalına ihtiyacı varsa, bu ihtiyaç ek PWM pinleri tanımlamak yerine modül üzerinde lokal üretim (örn. küçük bir MCU/FPGA) veya I2C üzerinden PWM sürücü/expander (örn. çok kanallı PWM driver) ile çözülmesi önerilir. Bu yaklaşım, qSlot v1.x geriye uyumluluğunu korurken kanal sayısını modül ölçeğinde esnek biçimde artırır.

PWM hatlarının frekans aralığı, çözünürlük ve “varsayılan duty” davranışı taşıyıcı kartın timer mimarisine bağlıdır. Bu nedenle PWM kullanan modüller, platform dokümanında tanımlanan frekans/drive limitlerine uyacak şekilde tasarlanmalı ve modül dokümanında beklenen aralıklar açıkça belirtilmelidir.

| Özellik | Değer |

|---|---|

| Hatlar | PWM1, PWM2 |

| Voltaj | 3V3 |

| Yön | giriş/çıkış (modüle göre) |

Ground (GND)

qSlot arayüzünde GND, sistemin ortak referansı olarak tek bir domain’de tanımlanır. Bu yaklaşımın amacı; modüller tak‑çıkar çalışırken referans seviyesinin parçalanmasını engellemek, geri dönüş akımlarının öngörülebilir kalmasını sağlamak ve sahada servis/yerleşim hatalarına karşı daha toleranslı bir topoloji oluşturmaktır.

Konektör üzerinde toplam 12 adet GND pini bulunur ve hedeflenen toplam dönüş akımı kapasitesi 6 A seviyesindedir. Bu kapasite, yalnızca pin sayısına bağlı değildir; taşıyıcı kartın GND plane sürekliliği, via yoğunluğu, konektör çevresindeki bakır dağıtımı ve güç hatlarına yakın konumlandırılmış dönüş yolları ile birlikte değerlendirilmelidir.

qSlot v1.0’da ayrı bir AGND domain’i tanımlanmaz. Gerekli olması durumunda 23 numaralı pin AGND olarak kullanılabilecektir. Bu şekilde kullanılması durumunda modül dokümanında mutlaka belirtilmelidir.

USB

USB_D+ / USB_D− hatları, yalnızca servis/test amaçlı bir veri kanalı olarak tanımlanır. Platformların çoğunda USB host/device rolü ve konnektör topolojisi değişken olabileceğinden, qSlot tarafında USB için “zorunlu bir güç dağıtımı” varsayımı yapılmaz; yalnızca diferansiyel veri çiftinin arayüzü sabitlenir.

USB kullanılacak platformlarda, hatların ESD koruması ve diferansiyel yönlendirme kuralları (eş uzunluk, kontrollü empedans, referans plane sürekliliği) platform tasarım kuralları içinde ayrıca ele alınmalıdır.

USB kullanılacaksa, USB beslemesi (VBUS) VCC üzerinden yeniden anlamlandırılmamalı; tasarımda açıkça yönetilen ayrı bir USB_VBUS_5V hattı planlanmalıdır. qSlot üzerindeki VCC, slot class ile tanımlı yardımcı beslemedir ve USB VBUS ile karıştırılması saha uyumluluğu açısından risklidir.

Tasarım kuralları

Bu bölüm, qSlot v1.0 uyumluluğunu korumak için hem taşıyıcı kart hem de modül tarafında uygulanması gereken en küçük tasarım kuralları setini özetler. Buradaki kurallar, belirli bir şema/topoloji dayatmak yerine; sahada en sık karşılaşılan arıza sınıflarını (ESD kaynaklı hasar, EMI kaynaklı kararsızlık, geri besleme ve yanlış besleme senaryoları) azaltmayı hedefler.

ESD ve saha dayanımı

qSlot arayüzü, saha kablolaması ve kullanıcı müdahalesi ile temas eden hatları barındırabildiğinden ESD dayanımı, uyumluluğun fiili bir parçasıdır. UART/I2C/SPI/DIO/PWM gibi dış dünyaya uzanan her sinyal hattı için ESD koruması SHOULD değerlendirilmelidir. Bu koruma yalnızca komponent seçimi değil, yerleşim stratejisi ile anlam kazanır: ESD elemanları konektör girişine mümkün olduğunca yakın yerleştirilmeli ve akım dönüş yolu kısa tutulmalıdır.

Taşıyıcı kart, qSlot’dan dış dünyaya çıkan hatların birincil koruma katmanı olarak konumlandırılmalıdır. Modül tarafında ise saha kablosuna yakın analog kaynaklar veya uzun kablo arayüzleri varsa ek koruma uygulanabilir.

EMI ve yönlendirme

qSlot üzerinde güç ve sinyal hatları bir arada taşındığı için yönlendirme kuralları, kararlılık ve ölçüm doğruluğu açısından kritiktir. POWER_FEED/VCC hatları geniş bakır ile taşınmalı, akımın döndüğü GND yolu düşük empedanslı ve sürekliliği yüksek plane üzerinden sağlanmalıdır. Analog hatlar (ANALOG1..4) mümkün olduğunca güç anahtarlama bölgelerinden, RF alanlarından ve hızlı kenarlı dijital hatlardan uzak tutulmalıdır.

I2C özelinde; pull‑up dirençleri ve toplam bus kapasitansı platform seviyesinde planlanmalı, modüllerin kontrolsüz şekilde pull‑up ekleyerek bus’ı ağırlaştırması engellenmelidir. Bu nedenle I2C buffer zorunluluğu, yalnızca adres/segment yönetimi için değil aynı zamanda bus yükünü kontrol edilebilir kılmak için de tasarım kararının parçasıdır.

Geri besleme önleme

Tak‑çıkar modüler sistemlerde en sık görülen sorunlardan biri, modül üzerindeki regülatör/boost gibi kaynakların 3V3 veya VCC hattını taşıyıcı karta istemsiz şekilde geri beslemesidir. Eğer platform mimarisi gereği geri besleme istenmiyorsa, modül tasarımında ideal diyot/ORing veya uygun bir güç anahtarı topolojisi ile geri akım yolları SHOULD engellenmelidir. Taşıyıcı kart tarafında da “enable=LOW iken hatların sürülmemesi” kuralı ile birlikte değerlendirilerek yarı‑açık çalışma durumlarının önüne geçilmelidir.

Şebeke (110/220VAC) qSlot konektörü üzerinden taşınması önerilmez. HV ölçüm/güç modülleri şebeke girişini ayrı klemens/konnektör üzerinden almalı; qSlot üzerinden yalnızca izole edilmiş düşük voltaj ve kontrol sinyalleri taşınmalıdır.

Sürümleme ve geriye uyumluluk

qSlot standardı sürümlenirken temel hedef, v1.x çizgisi boyunca geriye uyumluluğu koruyarak ekosistemin büyümesini mümkün kılmaktır. Bu nedenle pin haritası, domain kuralları ve normatif davranışlar (enable mantığı, I2C buffer zorunluluğu gibi) v1.x içinde kırıcı şekilde değiştirilmemelidir.

Yeni ihtiyaçlar ortaya çıktığında öncelik, mevcut arayüzü bozmadan genişletme yapmaktır: ayrılmış (reserved) alanların kullanılması, fonksiyonun mevcut bir arayüz üzerinden taşınması veya modül üzerinde expander/toplayıcı yaklaşımı bu kapsamda değerlendirilebilir. Pin anlamı veya elektriksel varsayım değişikliği gerektiren kırıcı değişiklikler ise v2.0 sürümüne saklanmalıdır.

Bu kütüphane, gerçek sahada kullanılan projelerden gelen ihtiyaçlara göre sürekli gelişen bir açık kaynak projedir. Kullanıcı geri bildirimleri, yeni fonksiyonların eklenmesi ve mevcut yapının iyileştirilmesi açısından kritik öneme sahiptir.

Bu kütüphaneyi hem kişisel hem de ticari projelerinde özgürce kullanabilirsin. Herhangi bir lisans kısıtı uygulanmamaktadır; amacım, bu kütüphanenin mümkün olduğunca fazla gerçek dünya projesinde yer almasıdır. Özel bir entegrasyon ihtiyacın, ticari bir planın veya teknik bir sorunun varsa bana e‑posta üzerinden her zaman ulaşabilirsin: akkoyun@me.com Geri bildirimlerini veya kullanım senaryolarını paylaşman, projeyi geliştirmem açısından büyük katkı sağlar.